LED(Light-emitting diode)由于寿命长、能耗低等长处被广泛地利用于唆使、显示等范畴。可靠性、稳固性及高出光率是LED代替现有照明光源必需考虑的因素。封装工艺是影响LED功效作用的重要因素之一,封装工艺关键工序有装架、压焊、封装。由于封装工艺本身的原因,导致LED封装过程中存在诸多缺点(如重复焊接、芯片电极氧化等),统计数据显示[1-2]:焊接系统的失效占全部半导体失效模式的比例是25%~30%,在国内[3],由于受到设备和产量的双重限制,多数生产厂家采用人工焊接的方法,焊接系统分歧格占分歧格总数的40%以上。从应用角度分析,LED封装过程中产生的缺点,固然应用初期并不影响其光电性能,但在以后的应用过程中会逐渐***露出来并导致器件失效。在LED的某些利用范畴,如高精密航天器材,其埋伏的缺点比那些立即呈现致命性失效的缺点迫害更大。因此,如何在封装过程中实现对LED芯片的检测、阻断存在缺点的LED进进后序封装工序,从而下降生产本钱、提高产品的质量、避免应用存在缺点的LED造成重大丧失就成为LED封装行业急需解决的艰苦。

目前,LED产业的检测技巧重要集中于封装前晶片级的检测[4-5]及封装完成后的成品级检测[6-7],而国内针对封装过程中LED的检测技巧尚不成熟。本文在LED芯片非接触检测方法的基础上[8-9],在LED引脚式封装过程中,利用p-n结光生伏殊效应,分析了封装缺点对光照射LED芯片在引线支架中产生的回路光电流的影响,采用电磁感应定律丈量该回路光电流,实现LED封装过程中芯片质量及封装缺点的检测。

1理论分析

1.1 p-n结的光生伏殊效应[m]根据p-n结光生伏殊效应,光生电流IL表现为:

式中,A为p-n结面积,q是电子电量,Ln、Lp分辨为电子和空***的扩散长度,J表现以光子数盘算的均匀光强,α为p-n结材料的接收系数,β是量子产额,即每接收一个光子产生的电子一空***对数。

在LED引脚式封装过程中,每个LED芯片是被固定在引线支架上的,LED芯片通过压焊金丝(铝丝)与引线支架形成了闭合回路,如图1。若疏忽引线支架电阻,LED支架回路光电流即是芯片光生电流IL。可见,当p-n结材料和掺杂浓度必定时,支架回路光电流与光照强度I成正比。

1.2封装缺点机理

LED芯片受到腐化因素影响或沾染油污时,在芯片电极表面天生一层非金属膜,产生封装缺点[11]。电极表面存在非金属膜层的LED芯片压焊工序后,焊接处形成金属一介质-金属结构,也称为隧道结。当必定强度的光照射在LED芯片上,若LED芯片失效,支架回路无光电流流过若非金属膜层足够厚,只有极少数电子可以隧穿膜层势垒,LED支架回路也无光电流流过;若非金属膜层较薄,由于LED芯片光生电流在隧道结两侧形成电场,电子重要以场致发射的方法隧穿膜层,流过单位面积膜层的电流可表现为[12]。

其中q为电子电量,m为电子质量,矗为普朗克常数,vx、vy、vz分辨是电子在x、y、z方向的隧穿速度,T(x)为电子的隧穿概率。又任意势垒的电子隧穿概率可表现为[13]

其中jin、jout。分辨是进进膜层和穿过膜层的电流密度,

,x指向为芯片电极表面到压焊点,为膜层中z方向任意点的势垒,E是垂直芯片电极表面速度为vx电子的能量。

,x指向为芯片电极表面到压焊点,为膜层中z方向任意点的势垒,E是垂直芯片电极表面速度为vx电子的能量。

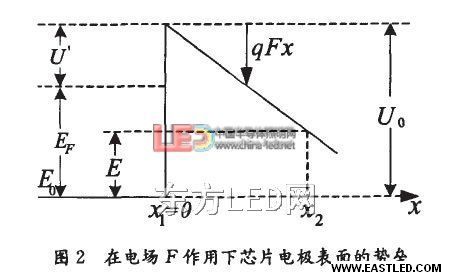

图2为在电场f’作用‘F芯片电极表面的势垒图,其中EF为费米能级,U,为电子发射势垒。由图

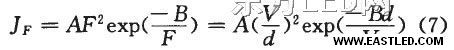

2,若芯片电极表面为突变结,其值为U0,光生电流在隧道结两侧形成的电场强度为F,电极表面以外的势垒为U0- qFx。取芯片电极导带底为参考能级E0(x=0),因而有x0处,U(x)=U0- qFx,根据条件U(x)=E=U0- qFx2

式中d为膜层厚度,V为膜层隧道结两侧电压。当LED芯片产生光生伏殊效应时,由式(7)可知,流过芯片电极表面非金属膜层的电流受到膜层厚度的影响,随着膜层增厚,流过膜层的电流减小,流过LED支架回路的光电流也将减小。

综上所述,引脚式LED支架回路光电流的有无或大小可以反应封装工艺中LED芯片的功效状态及芯片电极与引线支架的电气连接情况,因此,可以通过检测LED支架回路光电流达到检测引脚式封装工艺中芯片功效状态和封装缺点。

1.3封装缺点的检测方法

完成压焊工序后,LED处于闭合短路状态,直接导出回路电流进行检测不可行。固然支架回路有必定电阻,但光生电流只有微安量级,因而支架回路中的压降非常小,用一般的电压丈量方法难度较大,而且接触式检测会引进接触电阻,影响检测的准确性。因此,考虑用非接触式的电流检测方法。根据法拉第电磁感应定律,利用引脚式LED自身特点,检测时将带磁芯线圈中磁芯的一端插进图1所示闭合回路z中,LED支架回路作为一级绕组,带磁芯线圈作为次级绕组,并在线圈的两端并联上电容C,与线圈L组成LC谐振回路。以交变的光鼓励LED芯片时,支架回路中产生交变电流,交换载流回路会在四周空间产生交变磁场,次级线圈交变磁场则在次级线圈中产生感生电动势。若交变光频率与LC谐振回路频率相等时,LC回路产生共振,此时次级线圈两端感生电动势最大。因此,可以通过检测次级线圈两端感生电动势间接达到检测支架回路光电流的目标,实现对封装工艺中芯片功效状态及焊接质量的检测。

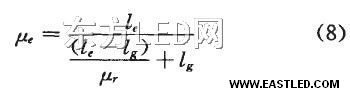

LC谐振回路中,线圈中磁芯起到加强磁感应强度B的作用,从而增加检测信号幅值。又线圈中磁芯的有效磁导率与相对磁导率间关系可表现为[14]:

式中,μe磁芯的有效磁导率,胁为磁芯的相对磁导率,μr为磁芯的有效磁路长度,名为非闭合气隙长度。

由式(8)可以看出,影响有效磁导率胁从而影响磁感应强度B的参数有:

①磁芯材料的相对磁导率胁。与所选软磁磁芯材料有关(软磁材料初始相对磁导率一般大于1000),当磁芯材料选定后,其相对磁导率为断定值。

②磁芯的有效长度le、非闭合气隙长度lg,它们由磁芯的结构决定。微弱电流产生的磁场易受外界因素干扰,磁路越长,干扰越大,所以磁芯的有效长度宜短。

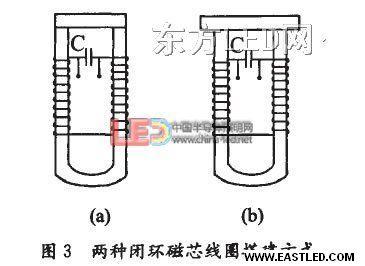

在磁芯材料断定的情况下,为了得到较大磁感应强度B,需转变线圈中磁芯的结构。若磁芯结构设计为环形,由式(8)知,磁感应强度B增大倍数理论上与磁芯的相对磁导率卢,大小相等,检测信号幅值将达到最大。与条形磁芯同种材质的u型磁芯上搭接一块条形磁芯就构成环形磁芯线圈,其搭接方法有两种,如图3示。

检测时将绕有线圈的U型磁芯的一端插进图1所示1闭合回路,感应LED支架回路中回路电流产生的交变磁通,再将条形磁芯搭接在U型磁芯上,使感应磁路闭合。由于搭接方法不同,两种搭接方法的磁芯线圈处在支架回路所产生的交变磁场中时,其搭接处磁路也将不同,用Ansoft Maxwell软件仿真两种搭接方法的磁芯搭接处在交变磁场中的磁回路,成果如图4示

图4中(a)、(b)仿真成果对应于图3中(a)、(b)两种线圈磁芯搭接方法。比拟两种线圈磁芯搭接处磁路仿真成果可以看出:①图3(a)示磁芯搭接处磁路在空气介质中的回路最短,所受磁阻最小,因此磁损耗也最小。②由于待测LED支架回路电流为微安量级,激起的磁场较小,易受空间电磁场的干扰,图3(b)示磁芯搭接处磁路***露在空气介质中较多,受干扰的几率较大。由上述分析,图3(a)磁芯搭接方法较优,可以加强信号检测端克制干扰才能,增加检测信号幅值,必定程度上提高光鼓励检测信号信噪比,进而提高缺点检测精度。

2实验及分析

2.1实验

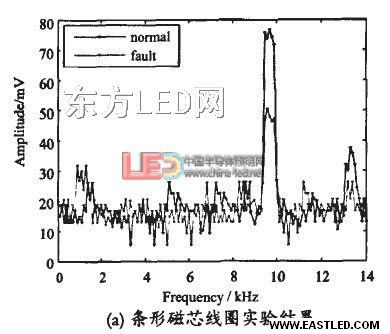

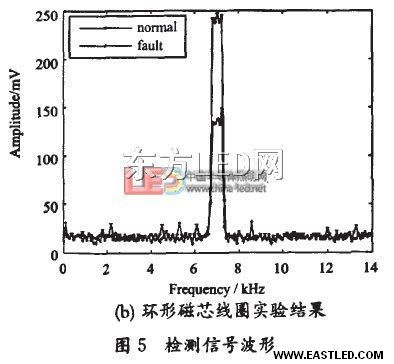

为了比拟条形磁芯线圈与环形磁芯线圈对封装缺点检测精度的影响,现分辨应用条形磁芯线圈和图3(a)示环形磁芯线圈进行实验。磁芯材料为PC40,其初始相对磁导率约为2300,条形磁芯的外形几何尺寸为1.6minx3.2ram×20mm,线圈匝数为300匝;环形磁芯横截面尺寸为1.6mm×3.2mm,其有效磁路长度约即是条形磁芯,线圈匝数为300匝。实验中鼓励光源为一种超高亮度贴片式白光LED,鼓励光源用占空比为50%的方波信号驱动,方波信号可由一系列正弦变更的信号叠加而成,使其基频与谐振回路的工作频率雷同,即LC谐振回路实现了对方波信号的选频,所以穿过线圈磁通链的变更率就是方波基频信号的变更率;检测对象分辨是GaP材料12mil黄色焊接质量合格的LED和焊接过程中芯片电极有非金属膜的LED。从线圈两端输出的信号经放大、滤波、峰值检波后见图5。实验中放大器的放大倍数为103倍。

2.2成果分析

本文先容的LED芯片封装缺点检测方法是通过检测LED支架回路光电流间接实现的。由图5可以看出,支架回路光电流激发的磁场在不同磁芯结构线圈两端感生电动势大小不同;不同磁芯结构线圈,检测信号的信噪比差别较大。具体表现为:

①焊接质量合格的LED,实验检测值与理论盘算值相吻合。图5(a)为应用条形线圈磁芯的实验成果,封装工艺中焊接质量合格的LED,信号检测端产生的光鼓励信号经放大、滤波、峰值检波后幅值约为60mV。选12mil黄色LED芯片进行理论值盘算,芯片面积A=0.3mm×0.3mm,取β=0.5当单位时间内单位面积被半导体材料接收的均匀光强(以光子数计)为5.45×1021个/m2s时,由式(1)可盘算出光生电流约为42μA。由毕奥-萨伐尔定理、叠加定理及法拉第电磁感应定律,可求得12mil黄色LED芯片在信号检测端感生电动势幅值约为63mV,往除实验误差和盘算误差,理论值和实验值较好地吻合。

②对于环形结构磁芯线圈,实验值较理论值小。根据式(8),对于条形结构磁芯线圈,假设磁芯有效磁路长度le=100lg,此时有效磁导率μe≈100。若磁芯改为环形,则非闭合气隙长度lg≈0,此时有效磁导率μe≈μr=2300,由理论盘算可知,12mil黄色焊接质量合格LED在信号检测端感生电动势幅值约为1.4V;由图5(b)知,实验得到信号值约为220mV,实验值远小于理论值。上述盘算是在幻想情况下进行的,在实际实验过程中,环形磁芯线圈是由U形磁芯和条形磁芯搭接而成的,搭接处气隙lg仍然存在,因而磁路不可能完整闭合,由式(8)知,气隙对有效磁导率影响很大,所以有效磁导率仍小于相对磁导率,因此,实验值远小于理论值。

③不同磁芯结构均可实现LED封装缺点的检测,但检测信号的信噪比差别较大。由图5可以看出,固然实验中磁芯线圈采用不同结构,对于焊接质量合格的LED,其光鼓励检测信号均明显大于封装过程中芯片电极表面存在非金属膜的LED光鼓励检测信号,通过比拟两者检测信号幅值的大小,可将封装过程中芯片电极表面存在非金属膜的LED捡出。对图5(a),实验应用的线圈中磁芯为条形结构,存在气隙lg,磁感应强度B加强倍数为有效磁导率μe,同时检测信号易受外界干扰,因而检测信号幅值较小且存在较大的检测噪声,使得两种芯片光鼓励信号信噪比都较小,给后端信号处理带来难度,影响封装缺点检测的准确度。将线圈中磁芯搭接成环形后构成闭合磁回路,磁感应强度B得到有效加强,磁损耗较小,受到空间电磁场的干扰相对也较小,所以检测信号信噪比得到明显改良。

④不同磁芯结构影响谐振回路的工作频率。实验过程中,LC谐振回路的电容C相等,环形磁芯的有效磁导率大于条形磁芯的有效磁导率,因而环形磁芯线圈的电感L大于条形磁芯线圈的电感,所以其谐振回路的谐振频率较小;从图5可以看出,条形磁芯线圈构成的谐振回路的谐振频率约为9.75kHz,而环形磁芯线圈构成的谐振回路的谐振频率约为7.33kHz。

⑤理论分析和实验成果分析可得,该方法对LED支架回路电流具有较高的检测精度,通过检测支架回路电流激起的磁场在线圈两端感生出电动势的大小,并与焊接质量合格的LED的检测信号进行比拟,实现对封装过程中存在封装缺点的LED进行检测。

3结论

针对引脚式LED芯片封装过程中存在的封装缺点标题,基于p-n结的光生伏殊效应,利用电子隧穿效应分析了一种封装缺点对LED性能的影响。理论分析表明,当LED芯片电极表面存在非金属膜层时,流过LED支架回路的光电流小于光生电流,随着膜层厚度的增加,回路光电流逐渐减小,其检测信号减小。通过非接触法检测待测LED光鼓励信号并与焊接合格的LED光鼓励信号进行比拟,实现对引脚式封装LED芯片在压焊工序中/后的功效状态及封装缺点的检测。分析了影响检测精度的因素。用焊接合格与芯片电极表面存在非金属膜的12mil黄LED样品进行实验,成果表明,该方法可以检测LED支架回路微安量级光生电流信号,并具有较高的信噪比,检测成果能实现对焊接质量合格与芯片失效或存在封装缺点的LED的区分,达到对LED芯片在压焊工序中/后的功效状态及封装缺点检测的目标,从而下降LED生产本钱、提高产品德量、避免应用存在缺点的LED造成重大丧失。

参考文献:

[1J张延伟,江理东.半导体器件典范缺点分析和图例[M].北京:科学技巧出版社,2004:11—22.

[2]田艳红,杭春进,王春青等.Cu丝超声球焊及楔焊焊点可靠性及失效机理的研究[J].电子工艺技巧,2006,27(2):63-69.

[3]丁荣峰,杨兵,任春岭等.第一次序键合引脚失效分析及键合可靠性提高[J].电子与封装,2005,8(5):1-5.

[4]Freeston IL.From Four Point to Impedance ImagingCJ].Engi—neering Science and Education Journal,1997,6(6):245—254.

[5]Tay C J.Su***ce Roughness Measurement of Semi-conductorWahrs Using a Modified Total Integrated Scattering Model[J].Int.J.Light and Electron Optics,2002,113(7):317—321.

[6]Kaminski A,Marchand J J,Laugier八I-V Method tO ExtractJunction Parameters with Special Emphasis on Low Series Resistanee[J].Solid-State Electron,1999,43:741—74533.

[7]王术军,张保洲.LED在线分拣系统的研制[J].半导体光电【j】,2004,25(2):108—111.

[8]李恋,李平,文玉梅等.LED芯片非接触在线检测方法[J].仪器仪表学报,2008,29(4):760—764.

[9]尹飞,李平,文玉梅等.LED芯片在线检测方法研究[J].传感技巧学报,2008,21(5):869-874.

[10]Miles R W,Hynes K M,Forbes L Photovohaic Solar Cells:anOverview of State-of-the-SArt Cen Development and Environ—mental Issues[J].Progress in Crystal Growth and C h a racterization of Materials,2005,51(1-3):1-42.

[11] Watanabe M,Tabuse D.Su***ce Contamination of BondingPads Incapable of Au Wire Bonding[C]//IEEE/CPMT InL ElectronManuhct Teehmol Symp,1998,187—193.

[12]曲喜新,过璧君.薄膜物理[M].电子产业出版社,北京,1994,228—229.

[13]舒启清.电子隧穿原理[M].科学出版社,北京,1998,30-31.

[14]赵凯华,陈熙谋.电磁学[M].高级教导出版社,北京,2001,55—59.

作者:

蔡有海(1982-),2005年毕业于重庆大学电子科学与技巧系,获学士学位,现于重庆大学光电工程学院攻读硕士学位,研究方向为仪器科学与技巧。

文玉梅(1964一),1984年毕业于北京航空航天大学电子工程系,获学士学位,1987年航天部第一研究院研究生院毕业获硕士学位,1997年重庆大学获博士学位。1988年起在重庆大学光电工程学院工作至今,教授,博士生导师。1999年至2000年英国牛津大学工程系高级拜访研究员。重要研究方向为传感器技巧,信号(图象)处理。